## JHPC-quantumシンポジウム2025

# テンソルネットワークを用いた 量子化学計算の大規模実機実行

菅野 志優

三菱ケミカル株式会社

2025年12月12日

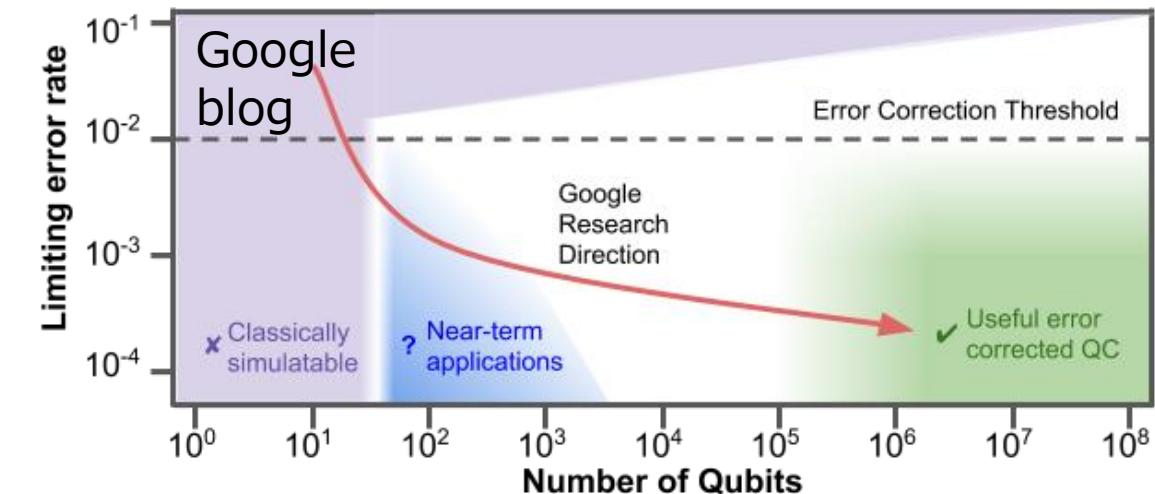

# 量子コンピューターの現状

- 古典コンピューターを超えるポテンシャル

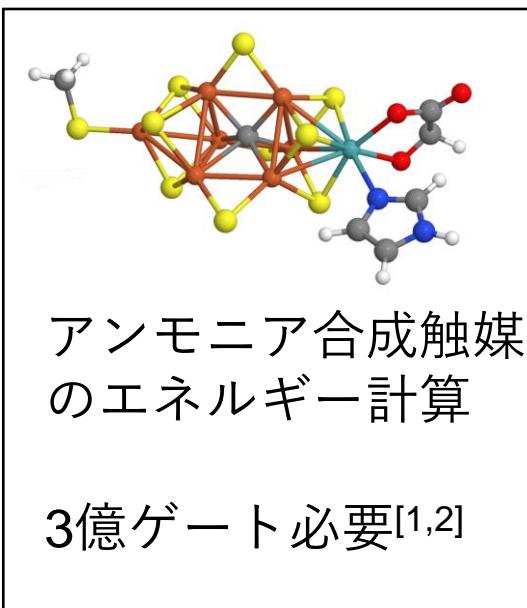

応用例：量子化学計算による分子設計

- 大規模化への過渡期

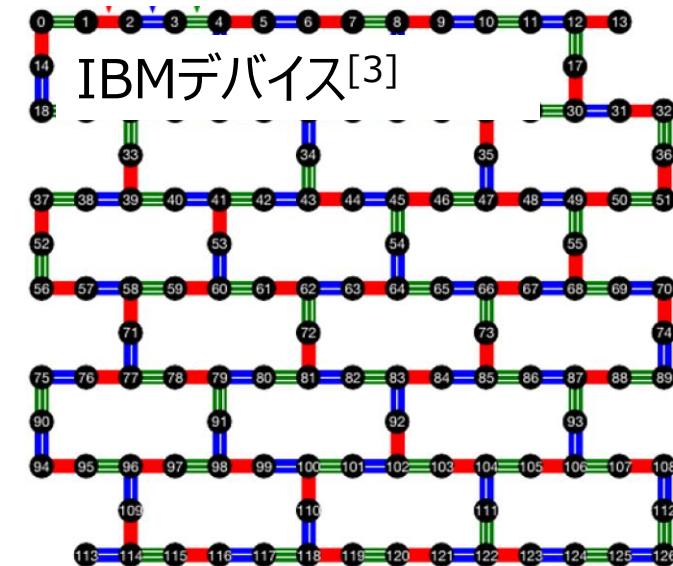

## 現在のスペック

量子ビット：10-1000

50量子ビットくらいで優位性

2量子ビットゲート：1,000-10,000

## 化学応用における課題

物理ノイズ

量子ビット間の接続

# プロジェクトの概要

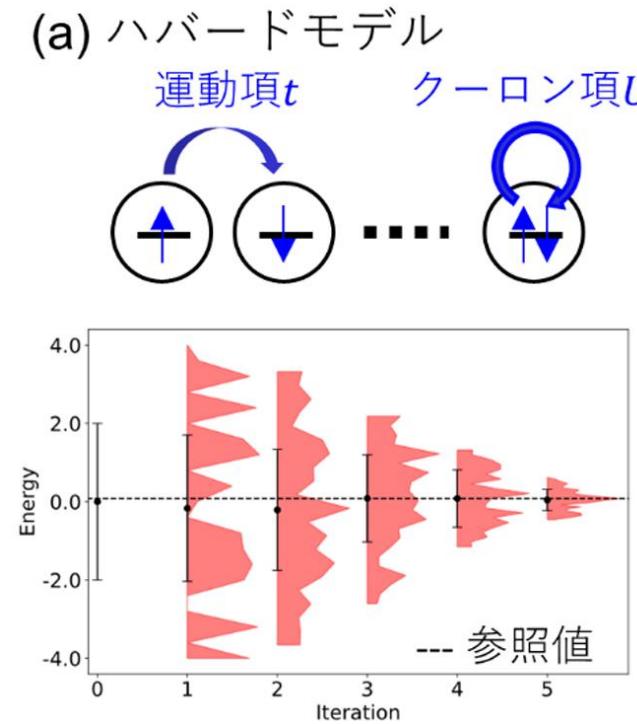

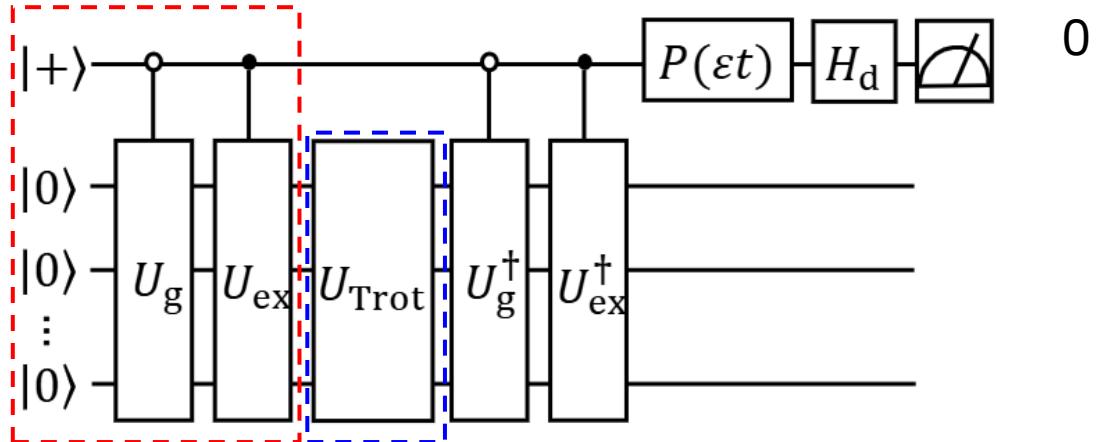

## 【これまでの研究】位相推定タイプのエネルギー・ギャップ・計算アルゴリズム

実機実行：最大32量子ビットの1次元ハバードモデル & 20量子ビットのポリエン

本プロジェクトではスパコン連携によりこのアルゴリズムの大規模化を検討する

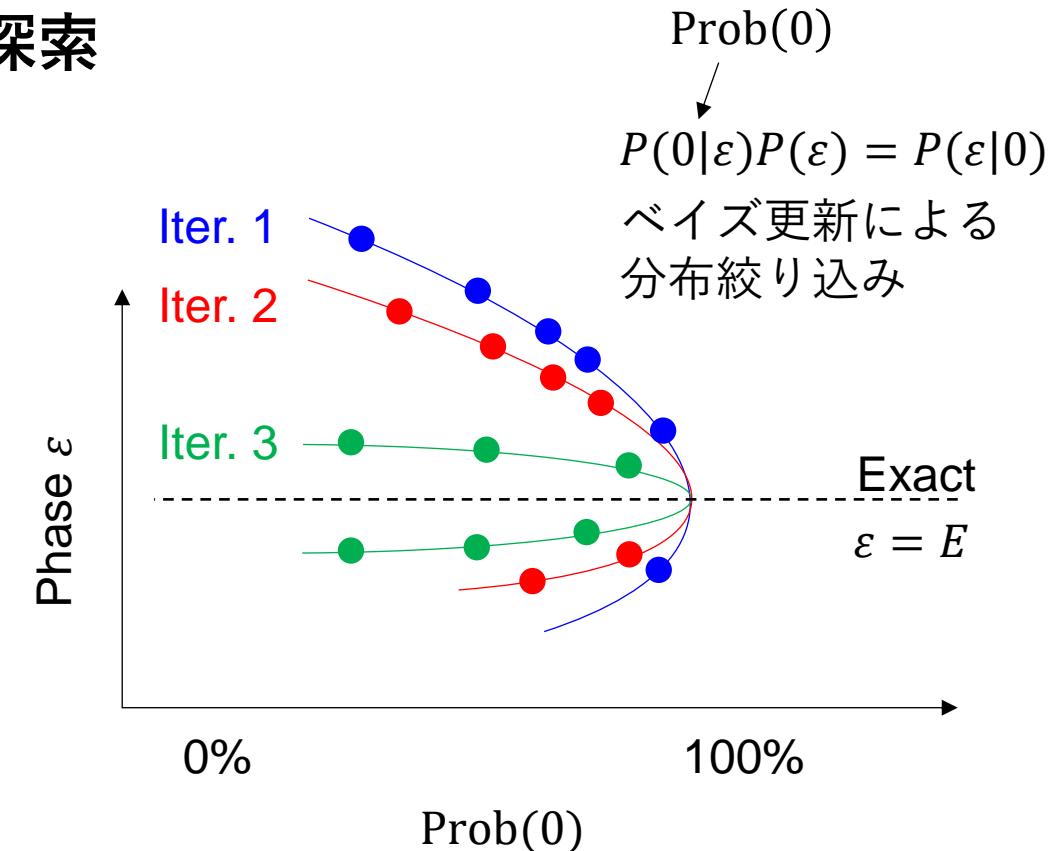

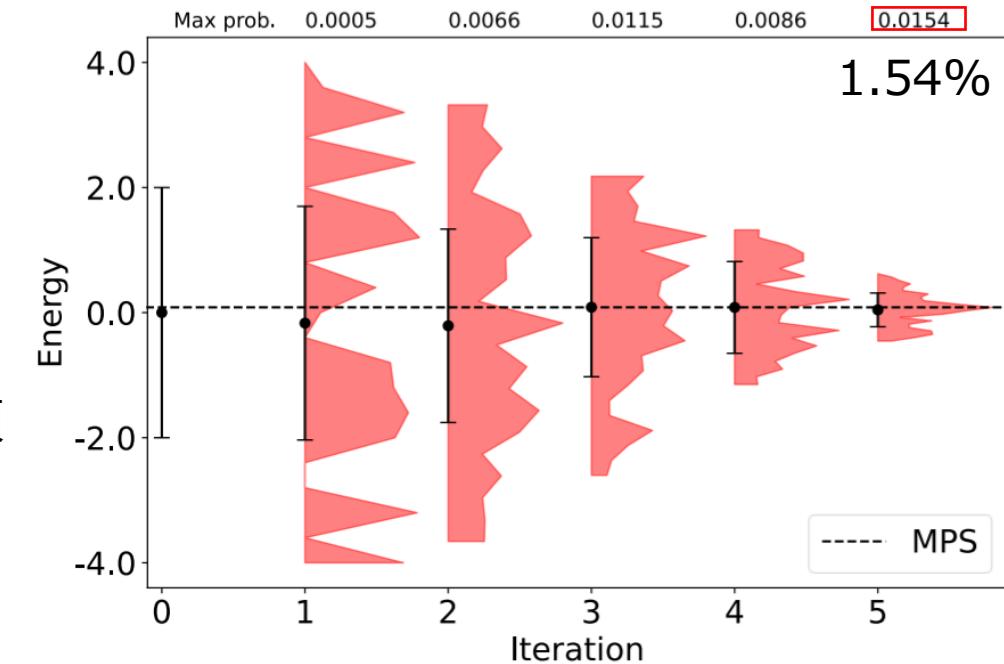

# 化学計算向けベイズ型量子位相推定 [1, 2]

基底状態などの、エネルギーに対応する位相 $\varepsilon$ を探索

## 課題

### 制御付き時間発展のコスト

多くの研究では2ビットシステム、最大6ビット [3]

[1] N. Wiebe, et al. Phys. Rev. Lett. **117**, 010503 (2016).

[2] K. Sugisaki, et al. Phys. Chem. Chem. Phys. **23**, 20152 (2021).

[3] N. S. Blunt, et al. PRX Quantum **4**, 040341 (2023).

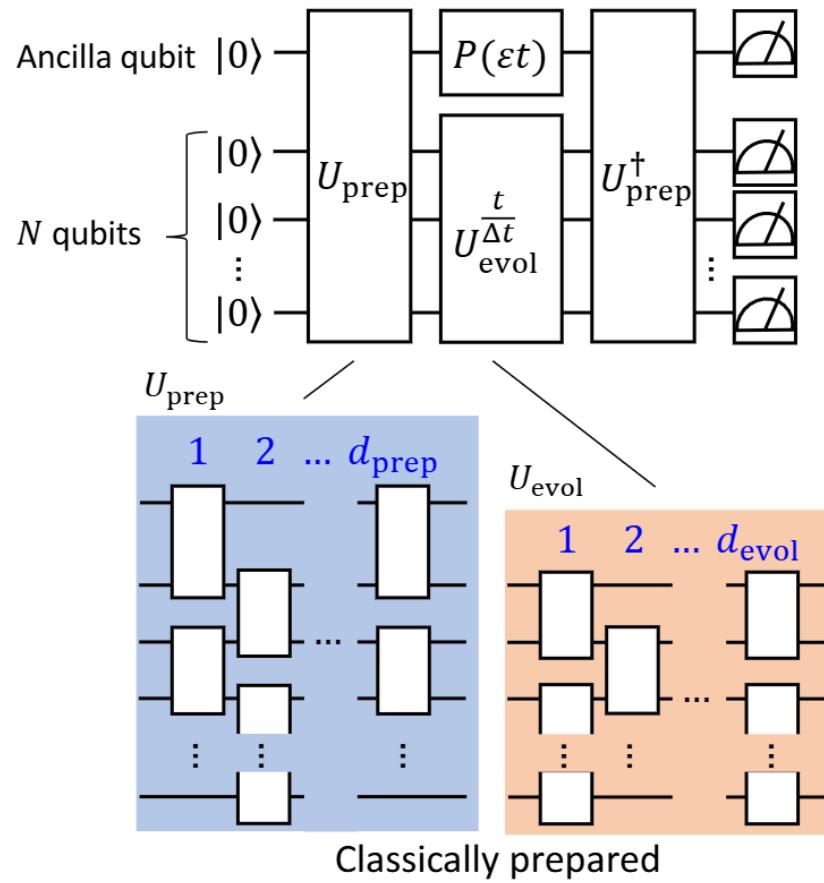

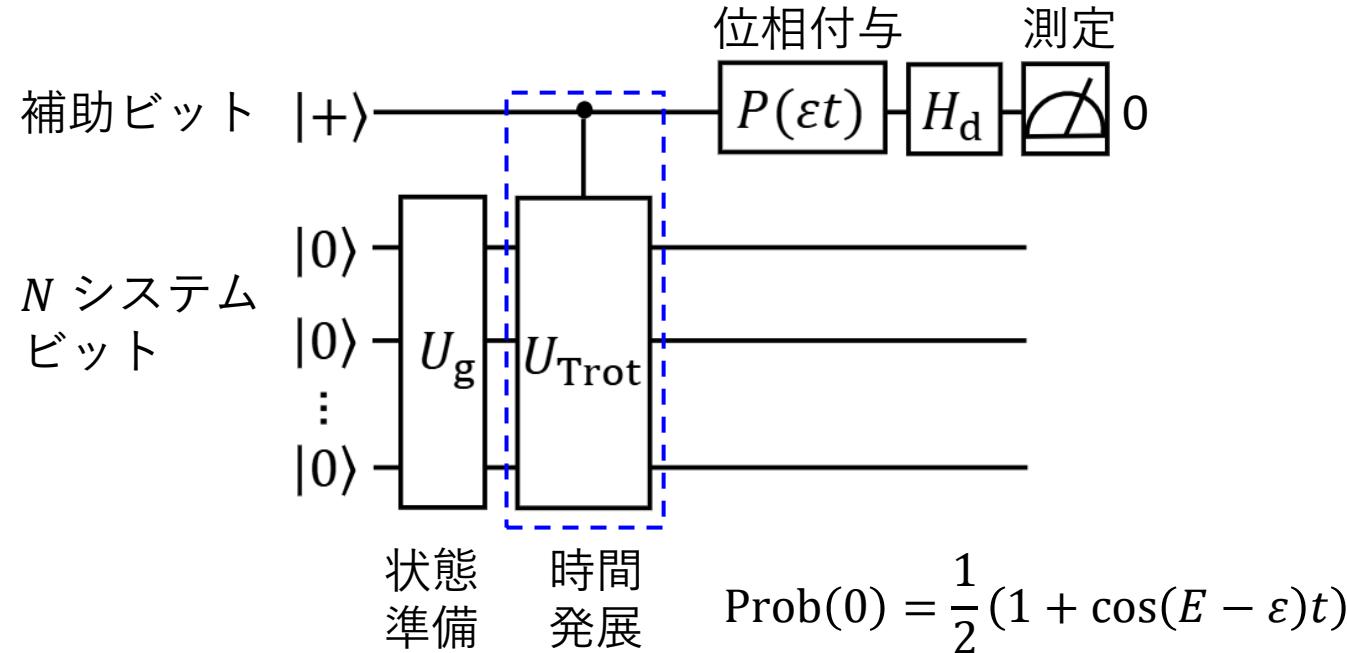

# 提案手法の特徴

## 量子位相差推定<sup>[1]</sup>

- **量子位相差推定の採用**

- エネルギーギャップ計算にフォーカス

- 制御付き時間発展の除去

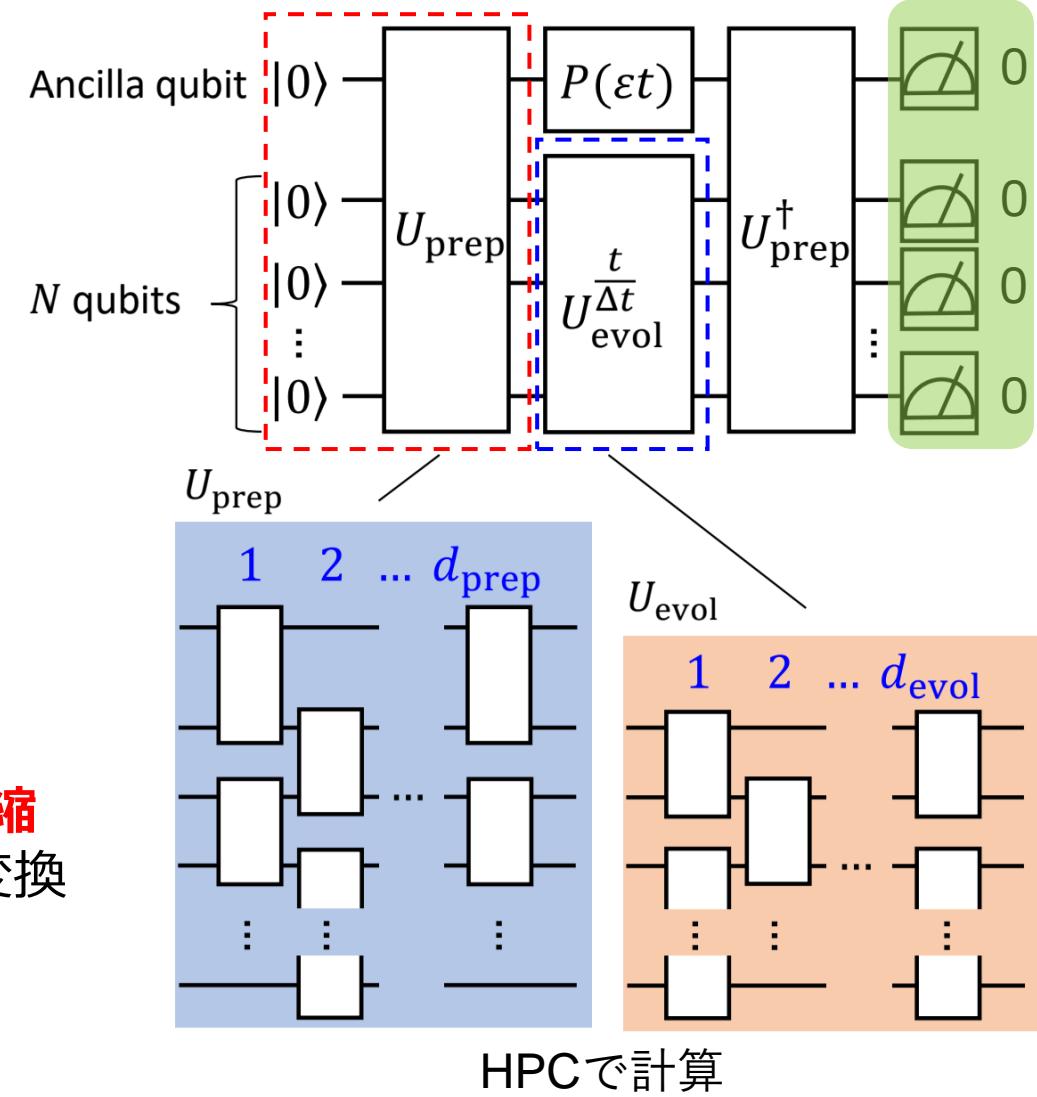

- **高性能計算 (HPC) によるテンソルを用いた古典回路圧縮**

- 超伝導デバイスで扱いやすい隣接ゲート構造に圧縮・変換

- 全ビット0測定によるノイズ混入の指數低減

## 提案手法

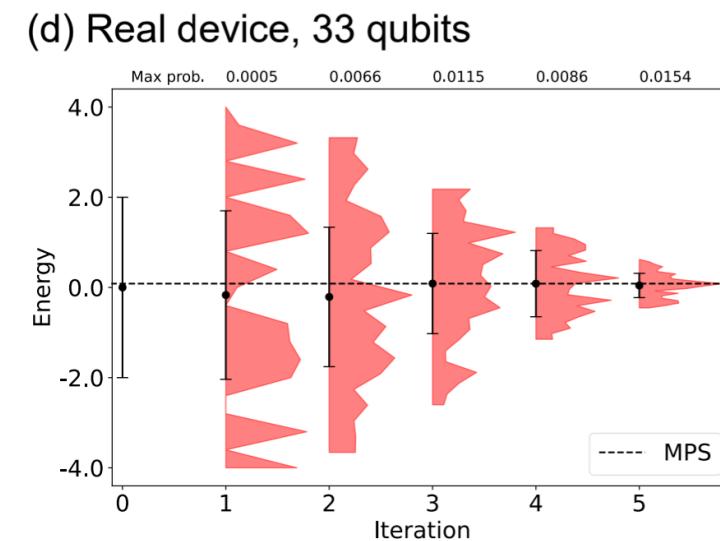

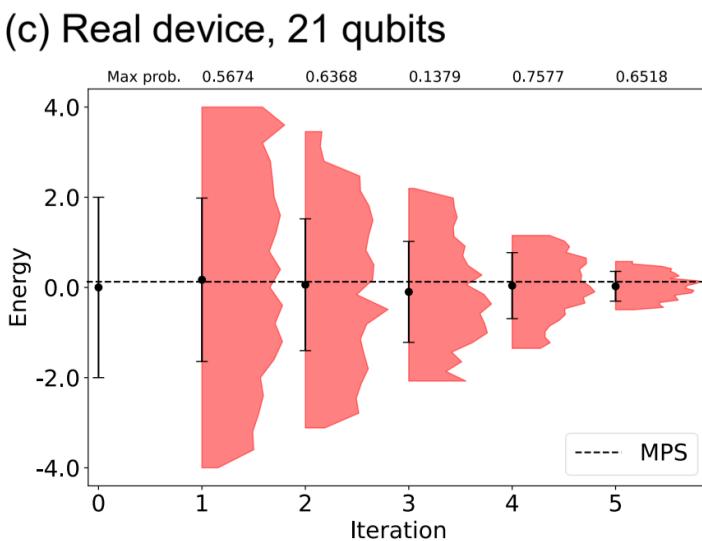

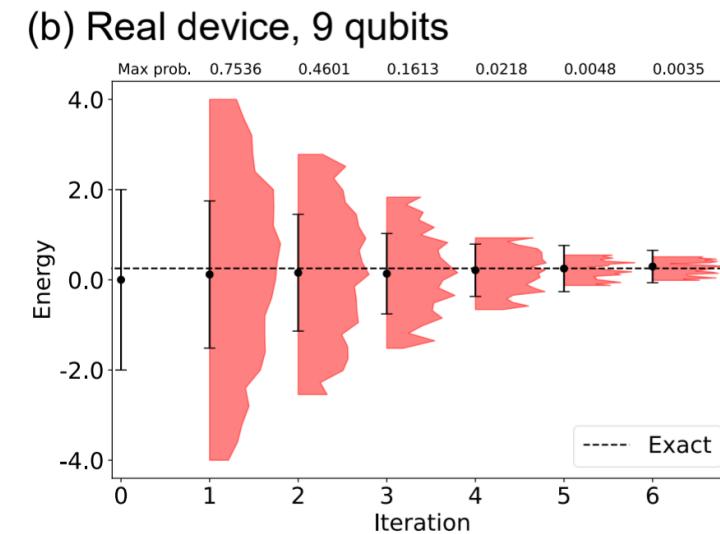

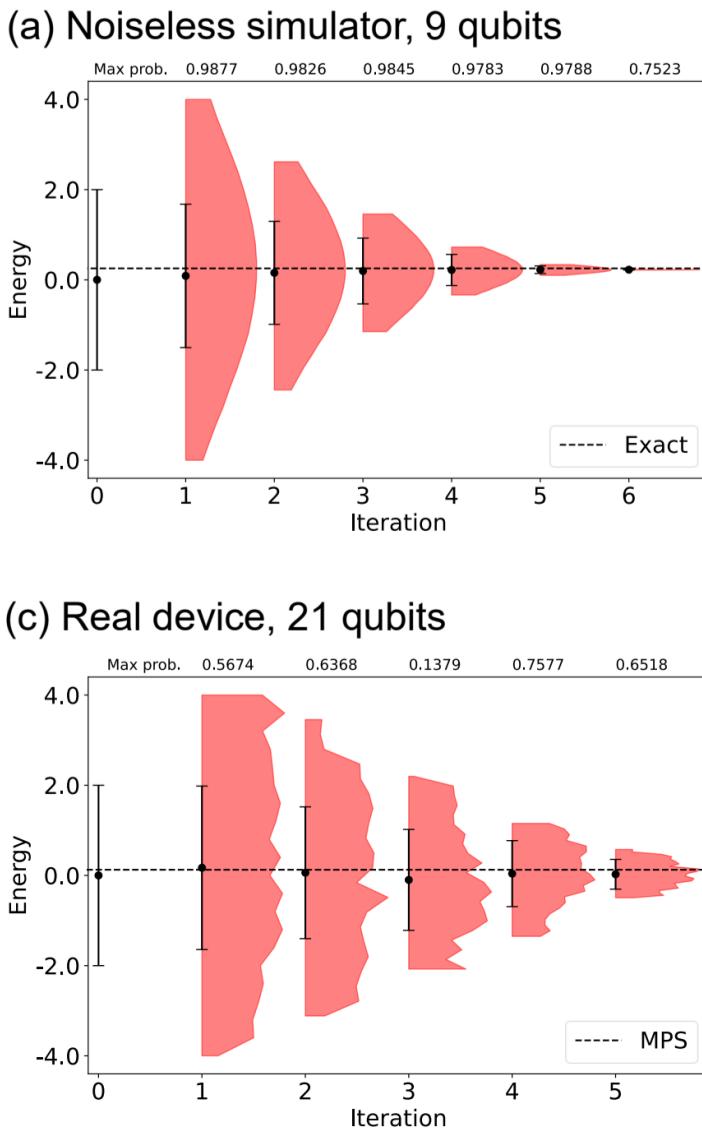

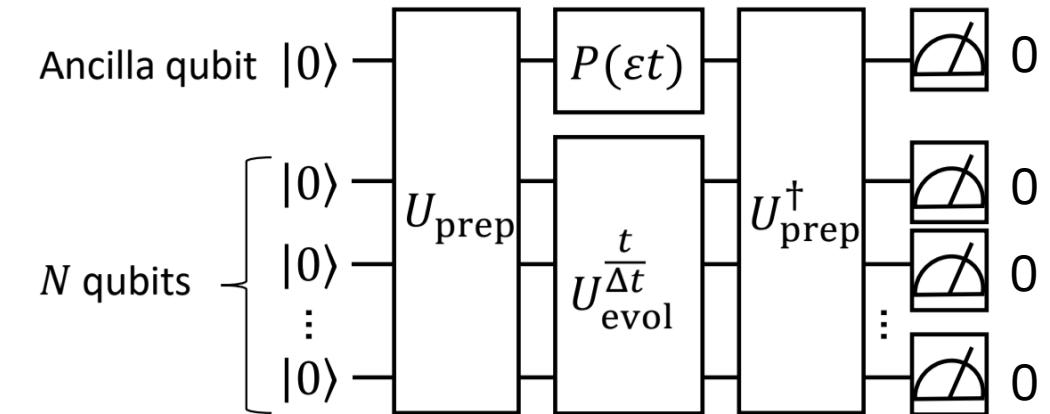

# Hubbardモデルの実行

- *IBM Heron*デバイスをQ-CTRLエラー抑制モジュールを通して実行<sup>[1]</sup>

- **32システムビットまで実行**

誤差は約40ミリHartree

- **先行研究<sup>[2]</sup>の5倍以上のサイズ**

# 大規模化成功の要因

## 回路の単純化

- 位相「差」推定による時間発展の制御除去

- HPCによるテンソル回路圧縮

- AIエラー抑制モジュール (Q-CTRL)

33量子ビットでは2量子ビットゲート数が

$7242 \rightarrow 794$

## エラー頑強性

- ・ ビット数に対しノイズ混入が指数減衰

- 実機検証では、シグナル1.5%でもピーク残存

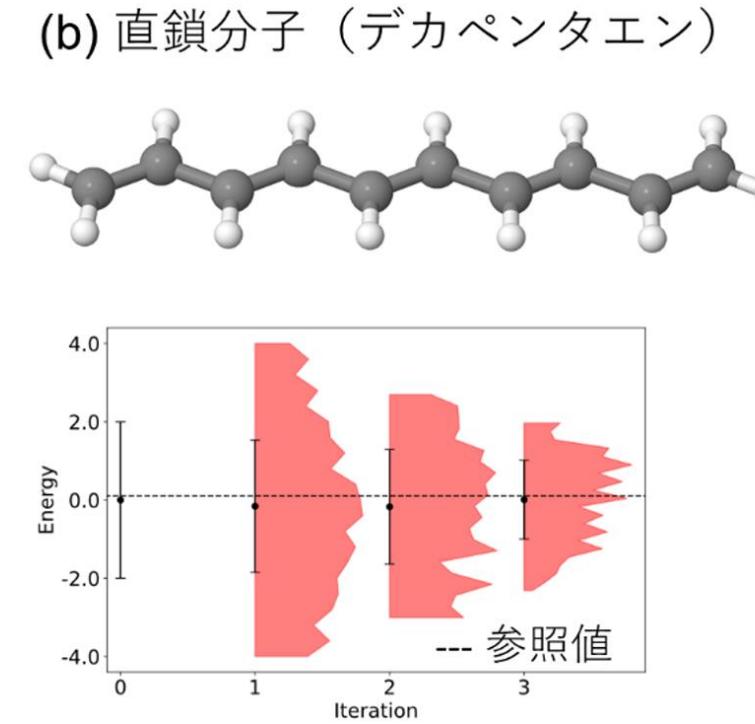

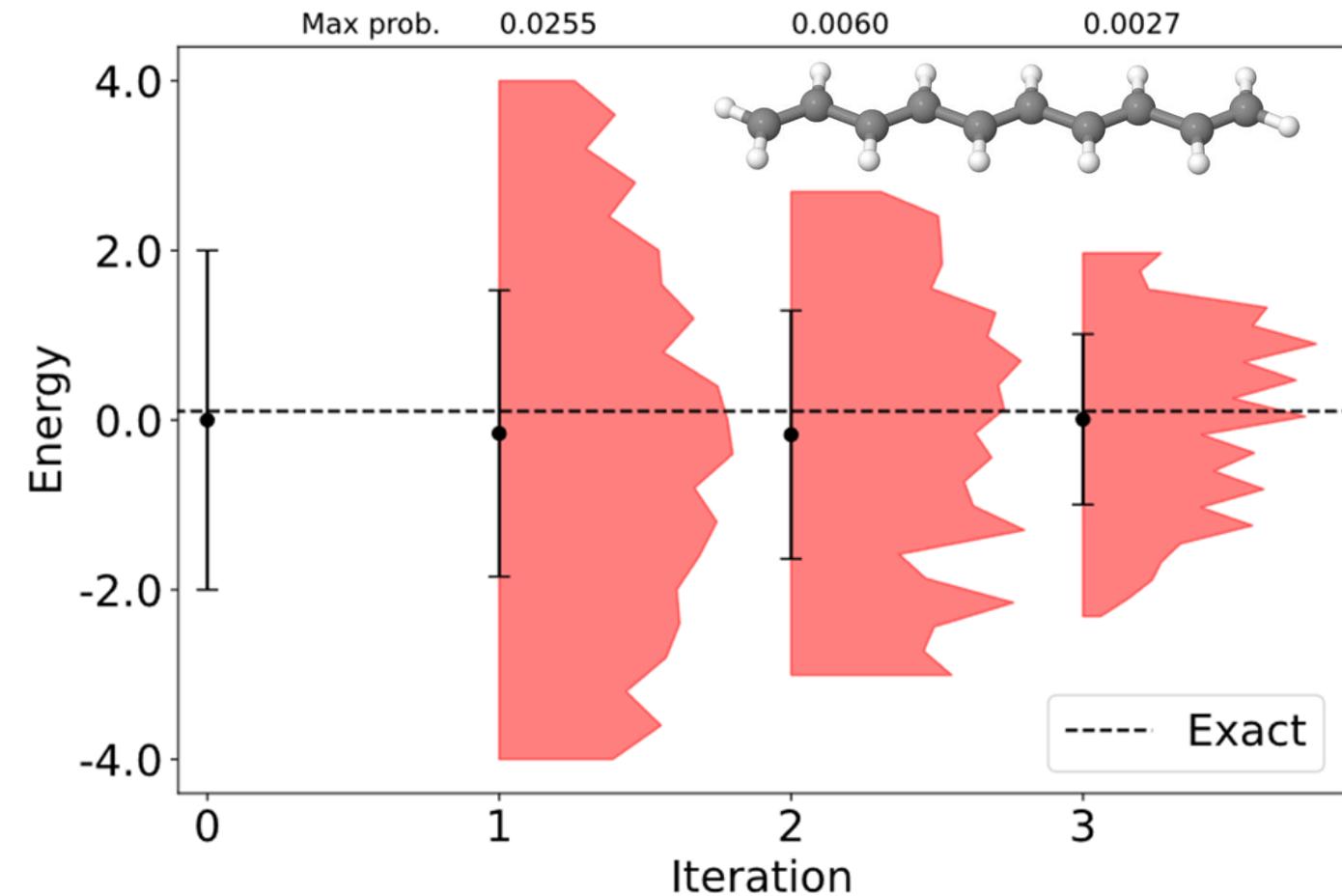

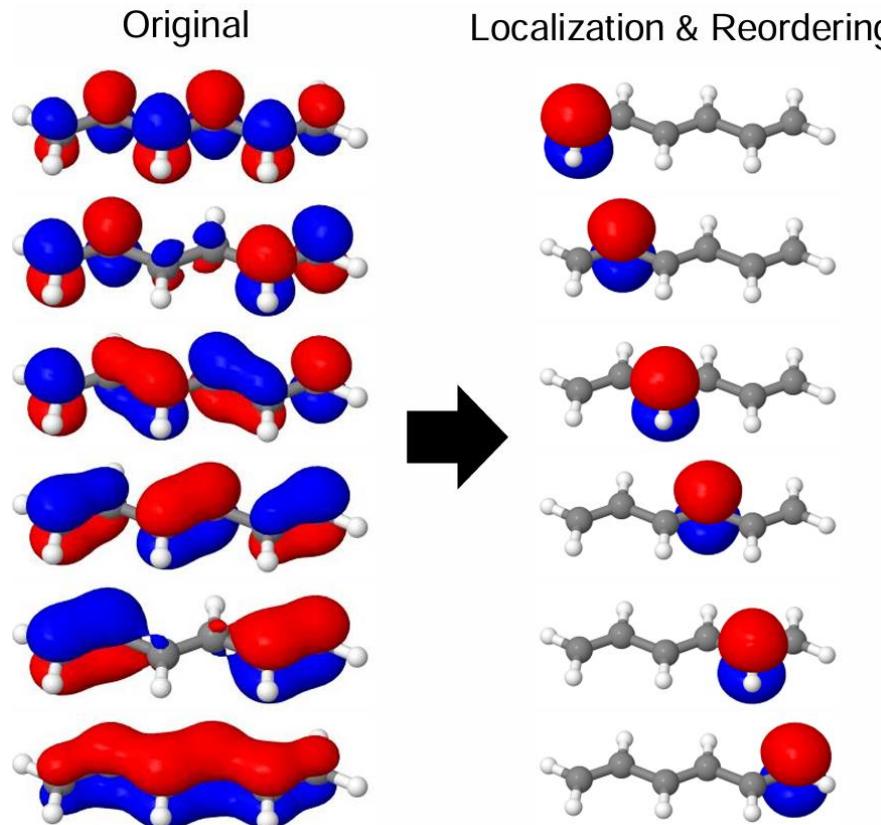

# ポリエンの実行 (21量子ビット)

分子軌道は非局在 → 軌道回転 + 並び替えで 1 次元に変換

量子計算の精度向上 & 古典処理軽減

# 本プロジェクトの目標

## これまでの研究<sup>[1]</sup>

テンソルに基づいた位相推定型のギャップ計算アルゴリズム

- 32量子ビットのハバードモデル、20量子ビットのポリエンで実機デモ

→従来（6量子ビット）の5倍以上の規模

## 目標

化学モデルを対象に、さらに大きな分子で位相推定したい

## 方針

- 最適化する回路をより深くして精度を上げる。富岳 or GPU上での並列化を想定

- 前処理、後処理の工夫