Work Packages

JHPC-quantum

07.

Research and Development of Quantum Circuit Optimization, and Error Collection and Mitigation

We will utilize HPC technology to reduce the impact of noise in quantum computing.

Overview

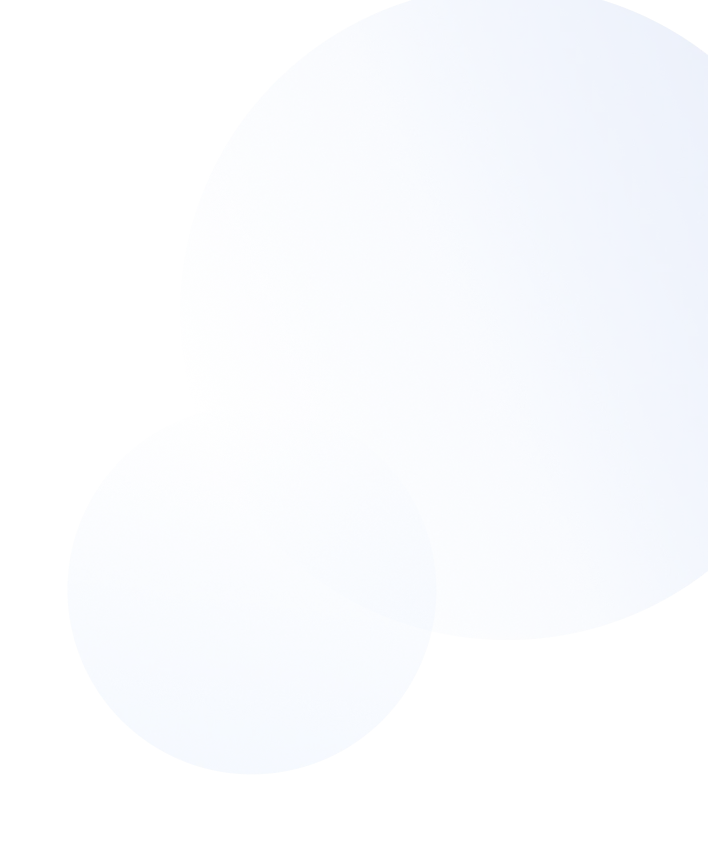

Current quantum computers are significantly affected by noise and face severe limitations in the number of qubits and quantum gates they can handle, making it challenging to apply quantum computing to various problems. To address this issue, we aim to maximize the performance of quantum computers by combining HPC technology with (1) quantum error suppression and mitigation techniques and (2) quantum circuit optimization techniques to minimize the influence of noise. This will expand the range of applications where quantum computers can be effectively utilized. Additionally, we will explore (3) quantum error correction technologies to develop sustainable quantum computing technologies.

Detail

The current NISQ (Noisy Intermediate-Scale Quantum) generation of quantum computers features tens to hundreds of qubits. Despite recent rapid technical advancements, these qubits are still not controlled well enough, leading to significant issues with noise and decoherence. Furthermore, these limitations make it difficult to perform quantum error correction, resulting in errors accumulating as quantum information is processed. Consequently, even though promising quantum computing methods have been theoretically proposed, their application on currently available quantum computers results in excessive errors, making it challenging to process quantum information and obtain meaningful results. This challenge is a major obstacle to the effective use of current quantum computers. To address this issue, we will leverage HPC technology to develop (1) quantum error suppression and mitigation techniques, (2) quantum circuit optimization techniques, and (3) quantum error correction techniques.

(1)Quantum Error Suppression and Mitigation Techniques

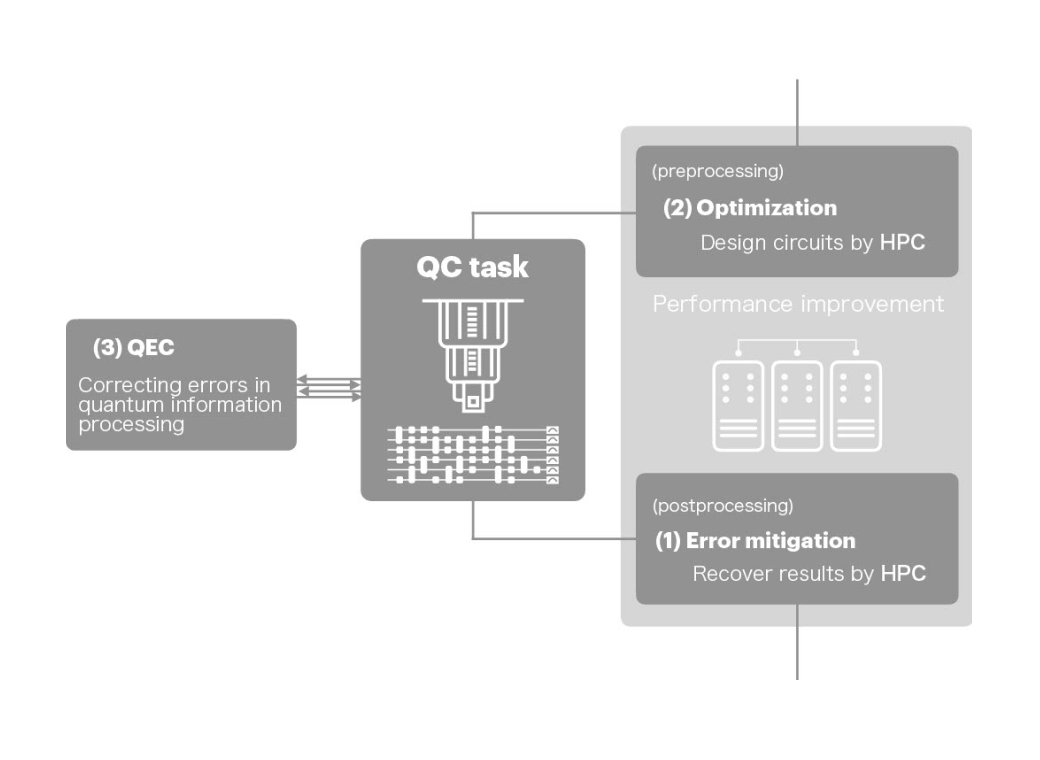

Quantum error mitigation techniques aim to reduce the impact of noise and errors on quantum computers and improve the accuracy of computational results. Unlike quantum error correction, which directly corrects errors during quantum information processing, error mitigation seeks to obtain more accurate results by modeling noise and reducing its impact on outcomes. Effective methods include zero noise extrapolation (ZNE), probabilistic error cancellation (PEC), and error reduction methods. Quantum error mitigation requires significant computational resources to gain insights into noise models by characterizing the nature of noise and evaluate results based on error mitigation techniques.

In this project, we will develop methods to effectively utilize HPC to enhance the performance of quantum error mitigation techniques, thereby expanding the range of quantum information processing that current quantum computers can perform.

Quantum error suppression focuses on reducing the sources of errors and decoherence, for example, by minimizing the number of gates used in a quantum circuit. Therefore, it is closely related to the items covered in (2) Quantum Circuit Optimization Techniques, described below.

(2)Quantum Circuit Optimization Techniques

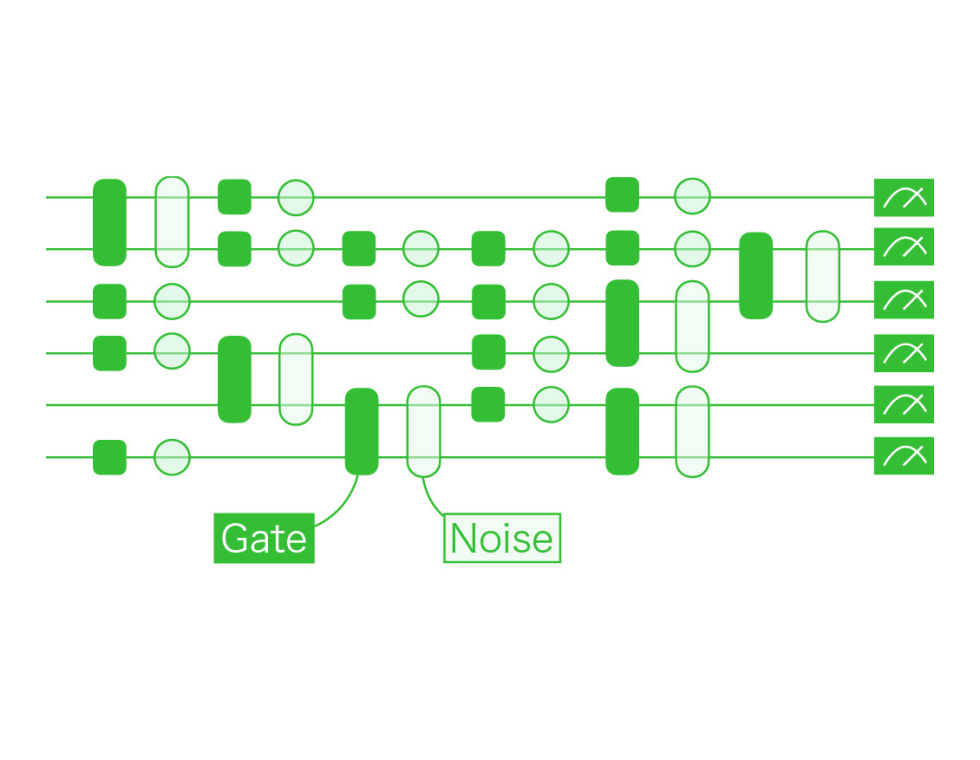

A direct method to reduce errors during quantum information processing is to effectively minimize the size of quantum circuits. Various quantum circuit optimization techniques have been proposed for this purpose. For instance, by appropriately partitioning quantum circuits and executing certain part of computations on classical computers, the number of qubits required by a quantum computer can be substantially reduced. Additionally, techniques include measuring certain qubits during quantum information processing, reinitializing them based on the measurement results, and reusing them to either shallow the quantum circuit or reduce the number of qubits needed. Another approach is to reconstruct quantum gate operations to reduce the number of quantum gates. However, the current methodologies face the challenge of exponentially increasing computation time, as the optimizations are processed on classical computers.

In this project, we will implement these quantum circuit optimization methods on a quantum-HPC integrated platform and evaluate their performance and effectiveness. Specifically, we will implement methods combining tensor network techniques-classical information compression technique-with various optimization methods from machine learning on the quantum-HPC integrated platform, aiming to develop scalable quantum circuit optimization methods that are effective for quantum circuits with over 100 qubits.

(3)Quantum Error Correction Techniques

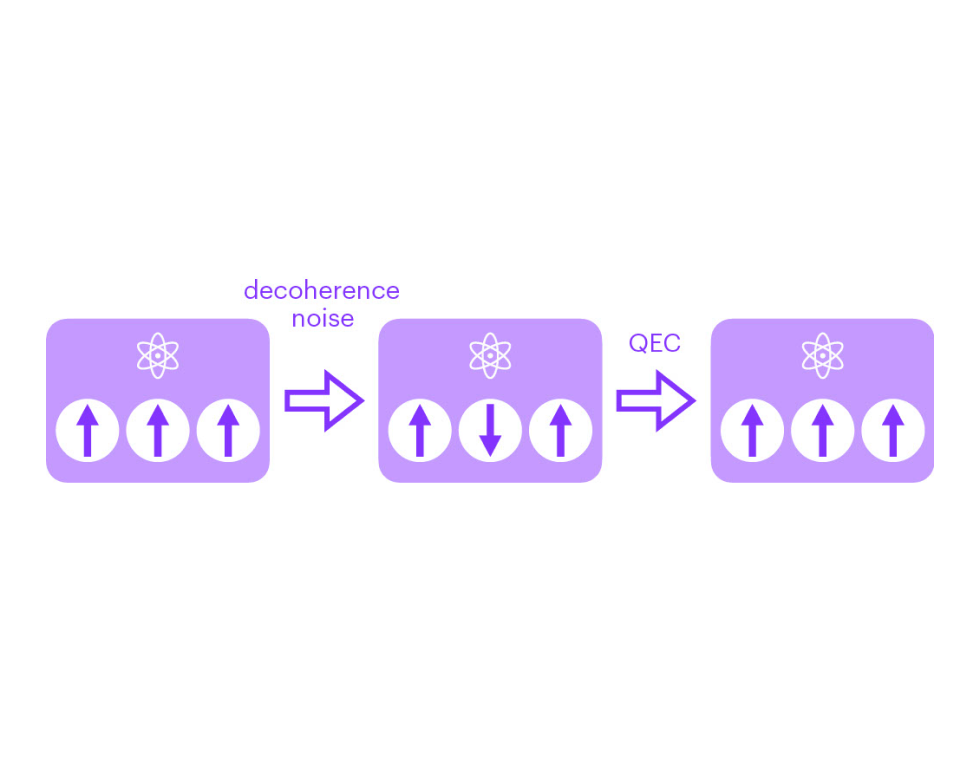

The ultimate quantum computer that surpasses the limitations of NISQ computers is the fault-tolerant quantum computer (FTQC), which encodes logical qubits using multiple physical qubits to detect and correct errors. Unlike NISQ computers, FTQC can handle computations on various scales, leading to numerous technical challenges. However, the research is rapidly advancing at various levels, from quantum devices to quantum error correction (QEC) techniques. Current quantum computers do not meet the QEC requirements in terms of error rates, making it difficult to demonstrate FTQC using NISQ-designed quantum computers. Nevertheless, investigating the technical possibilities and challenges of future FTQC using currently available quantum devices and systems is highly valuable.

In this project, we will explore the applicability and challenges of quantum error correction processing using currently available quantum computers. We will study the error rates of devices, the required encoding methods, and the applicability and technical challenges of these encoding methods. This research will provide insights that contribute to the future development of quantum computers and the advancement of FTQC research.

Project Members

RIKEN Center for Computational Science

Project Leader

- Seiji Yunoki

- Computational Materials Science Research Team

- Toshiyuki Imamura

- Large-scale Parallel Numerical Computing Technology Research Team

- Jan Erik Reinhard Wichmann

- Processor Research Team

- Kentaro Sano

- Processor Research Team

- Tomonori Shirakawa

- Computational Materials Science Research Team

- Sun Rongyang

- Computational Materials Science Research Team