事業項目 Work Packages

JHPC-quantum

07.

量子・HPC連携プログラム最適化技術の研究開発

HPC技術を駆使して、計算結果に対する量子コンピュータのノイズの影響を低減し、利用可能領域の拡大を推進します

概要overview

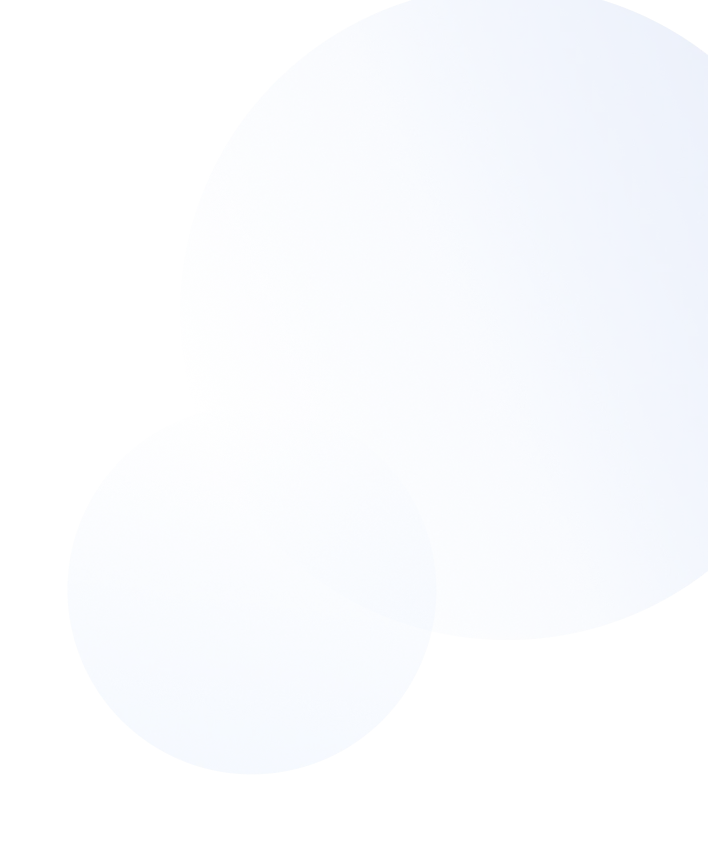

現在の量子コンピュータは、ノイズの影響が大きく、扱える量子ビット数や量子ゲート数に厳しい制限があるため、多様な問題に利用することが困難です。この問題に対処するため、HPC技術と(1)量子エラー抑制・緩和技術と(2)量子回路最適化技術を組み合わせることで、量子コンピュータのノイズの影響を極力軽減し、その性能を最大限に引き出すことを目指します。これにより、量子コンピュータが利用可能な領域の拡大を推進します。さらに、持続可能な量子コンピューティング技術の開発に向け、(3)量子エラー訂正の研究開発にも取り組んでいきます。

事業内容detail

現在利用可能なNISQ(Noisy Intermediate-Scale Quantum)世代の量子コンピュータの特徴は、数十から数百の量子ビットを持ち、技術的な問題で量子ビットが非常に繊細であるためノイズとデコヒーレンスの問題があるものとなっています。さらに、こうしたノイズやデコヒーレンス、量子ビット数の制限などにより、エラー訂正を行うことが難しいため、エラーがそのまま蓄積する状況になっています。したがって、理論的に有望な量子コンピュータの利用方法があっても、それを現在利用できる量子コンピュータ実機で用いると、エラーが大きすぎて量子情報を扱うことが困難となり、意味のある結果が得られない、と言った問題が発生します。この問題は、現在利用できる量子コンピュータ実機を利用することが困難となる主要因となっています。そこで、こうしたノイズの影響をHPC 技術によって抑制するための手段として、我々は

(1)量子エラー抑制・緩和技術、(2)量子回路最適化技術、および、(3)量子エラー訂正技術の研究開発に取り組みます。

(1)量子エラー抑制・緩和技術

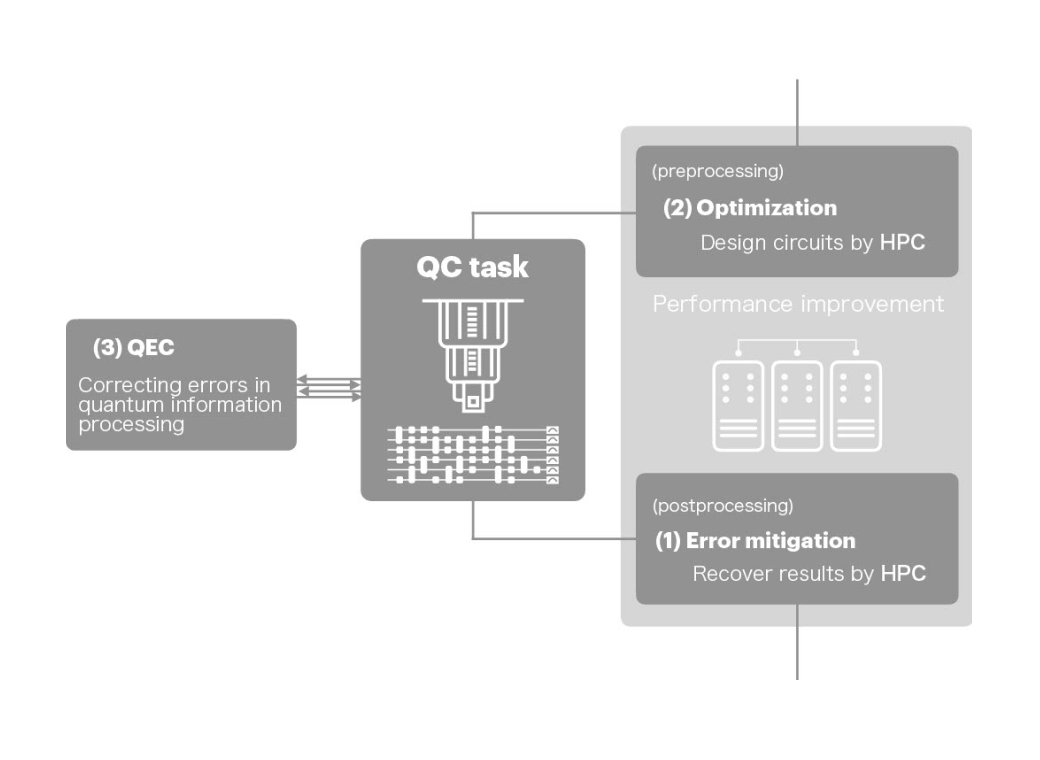

量子エラー緩和技術とは、量子コンピュータが抱えるノイズやエラーの影響を軽減し、計算結果の精度を向上させる技術です。量子エラー訂正とは異なり、エラーそのものを修正するのではなく、ノイズをモデル化して、観測結果に対してその影響を減らすことで、より正確な計算結果を得ることを目的とします。代表的な方法として、Zero Noise Extrapolation(ZNE)、確率的エラーキャンセレーション(Probabilistic Error Cancellation, PEC)、エラーリダクション法(Error Reduction Methods)などの有効性のある方法が知られています。量子エラー緩和技術では、ノイズモデルの洞察や、エラー緩和技術をもとにした値の評価などに大きな計算機資源が必要となります。

そこで、本課題では、HPCを有効的に利用できる手法の開発を行い、量子エラー緩和技術の性能向上を図ることで、量子コンピュータが実行できる量子情報処理の範囲拡大を目指します。

量子エラー抑制とは、ゲート数などを減らすなどにより、量子エラーやデコヒーレンスが起こりにくくすることで、以下の「(2)量子回路最適化技術」に関係しています。

(2)量子回路最適化技術

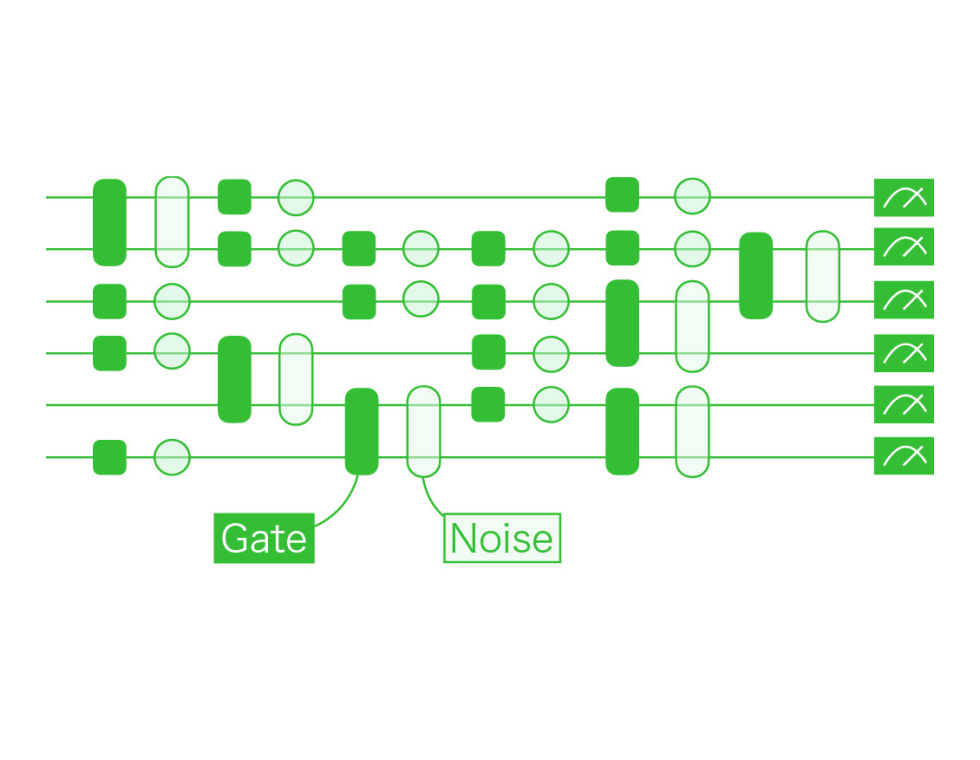

量子情報処理の過程でエラーを低減するための直接的な方法は、量子回路の規模を実効的に小さくすることです。そのために、様々な量子回路最適化技法が提案されています。例えば、量子回路を適宜分割して一部の演算を古典コンピュータで実行することで、量子コンピュータで扱う量子ビット数を実質的に減らす方法があります。また、量子情報処理の途中でいくつかの量子ビットに対して観測を行い、その結果に従って観測した量子ビットを再利用することで、量子回路を浅くしたり量子ビット数を少なくする方法や、量子ゲート操作を適宜再構成することで量子ゲート数を減らす方法もあります。ただし、現状の方法論では、量子ゲートや量子状態の情報を古典コンピュータで扱うため、計算時間が指数関数的に増大するという課題があります。

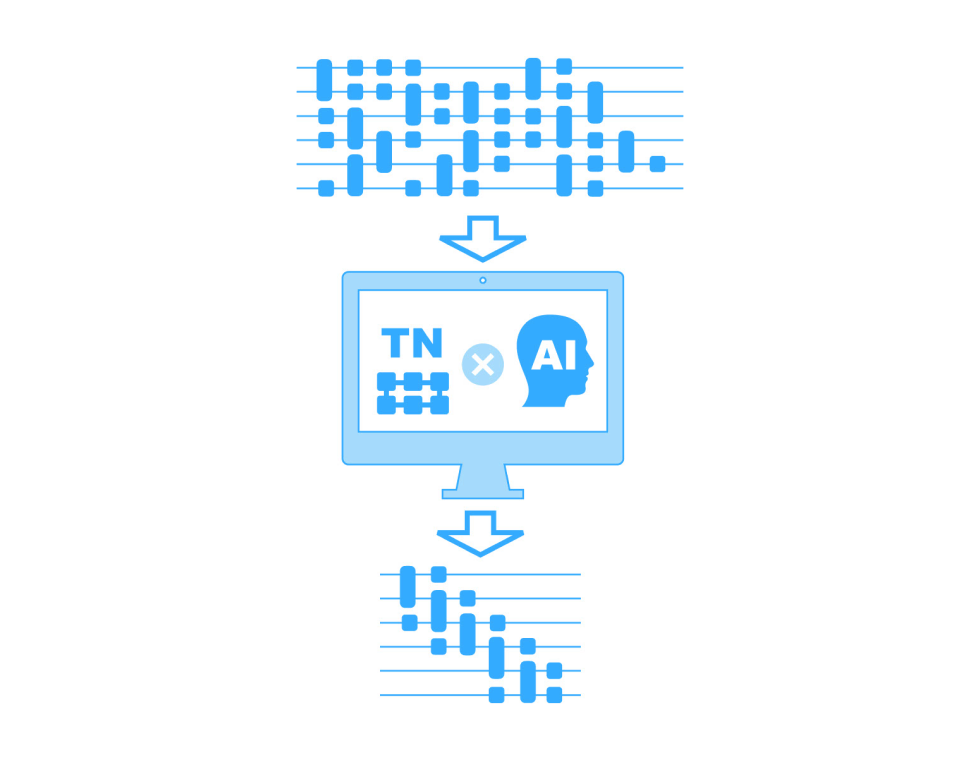

そこで、本事業項目では、これらの量子回路最適化法を量子・スパコン連携プラットフォームに実装し、その有効性を評価します。特に、本課題では、テンソルネットワーク法と呼ばれる古典情報圧縮技術や、機械学習分野のさまざまな最適化技術を組み合わせた方法などを量子・スパコン連携プラットフォームに実装することで、100量子ビット以上の量子回路にも有用な、スケーラブルな量子回路最適化法の開発を行います。

(3)量子エラー訂正技術

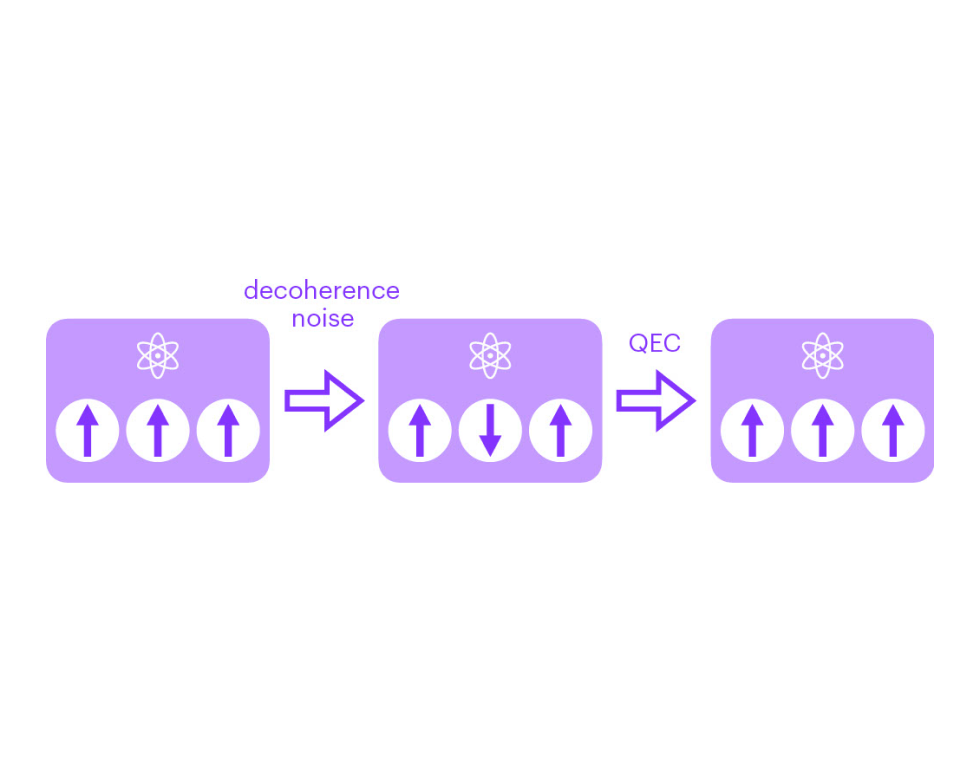

NISQコンピュータの限界を超えた究極の量子コンピュータは、多数の物理量子ビットを使って論理量子ビットを符号化し、エラーを検出および訂正する「誤り耐性を持つ量子コンピュータ(FTQC)」です。NISQコンピュータと比べて様々な規模の計算が可能になるため、技術的な課題は多くありますが、量子デバイスから量子エラー訂正(QEC)技術に至る様々な階層で、FTQCの研究が進められています。現行の量子コンピュータはエラー率などの点でQECの要件を満たしていないため、現行の量子コンピュータを用いてFTQCを実証することは困難です。しかしながら、現在動作する量子デバイスやシステムを用いて将来のFTQCの技術的可能性や課題を調査することは意義深いです。

そこで、本事業項目では、現行の量子コンピュータを用いて、QEC処理の適用可能性や課題について調査します。デバイスエラー率やそれに必要な符号手法、あるいや符号手法の適用可能性や技術的課題を調査し、量子コンピュータの今後の発展とFTQC研究の進展に貢献し得る知見を得ます。

プロジェクトメンバーproject members

理化学研究所計算科学研究センター

プロジェクトリーダー

- 柚木 清司

- 量子系物質科学研究チーム

- 今村 俊幸

- 大規模並列数値計算技術研究チーム

- Jan Erik Reinhard Wichmann

- プロセッサ研究チーム

- 佐野 健太郎

- プロセッサ研究チーム

- 白川 知功

- 量子系物質科学研究チーム

- Rongyang Sun

- 量子系物質科学研究チーム